# Thermo-Mechanical Optimisation of Press Pack IGBT Packaging using Finite Element Method Simulation

Michael Varley, Ashley Plumpton, Chas Tonner, Robin Simpson

#### Introduction

Design of Press Pack IGBT packaging needs to take into consideration of a number of requirements:

- 1. Protection of the IGBT structure

- 2. Minimisation of bulk stress in the IGBT

- 3. Minimisation of thermal resistance

- 4. Maximisation of compliance

- 5. Maximisation of reliability

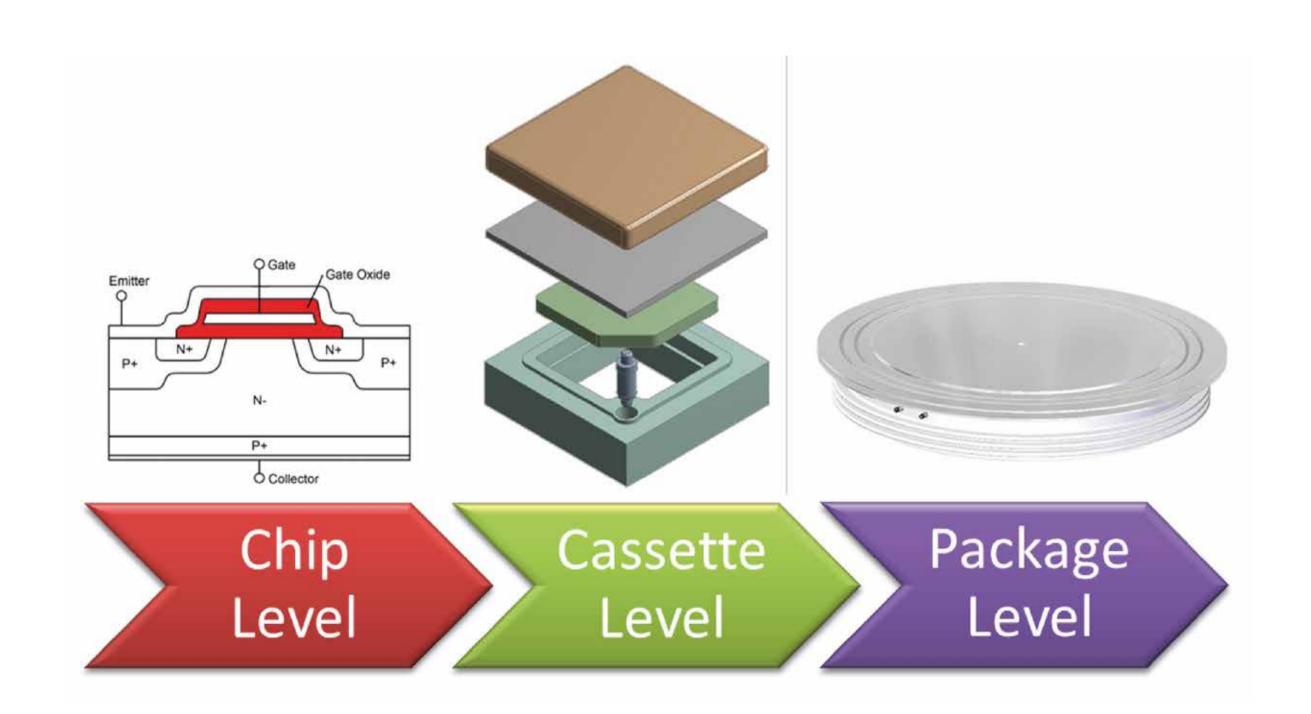

These represent chip, cassette and package level requirements.

### Stages of Press Pack Optimisation

### Chip Level Optimisation

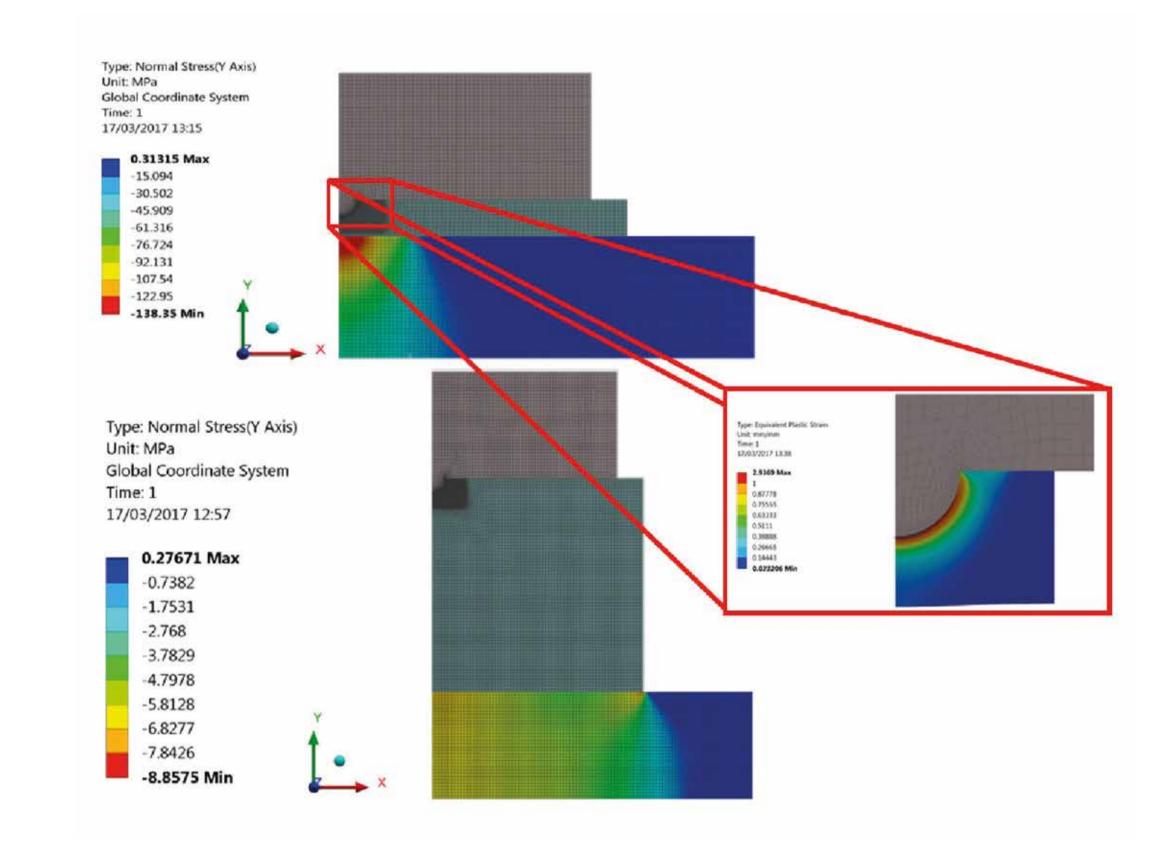

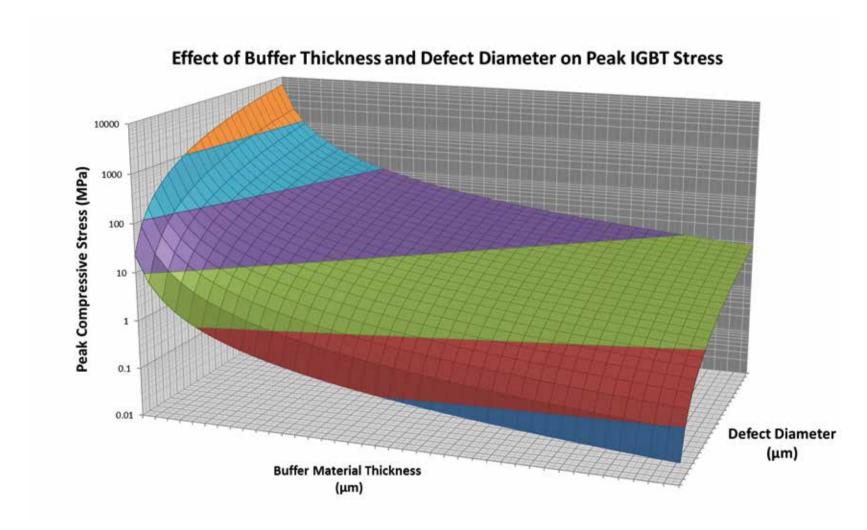

- Microscopic defects on components reduces electrical performance, and can lead to failure of the chip.

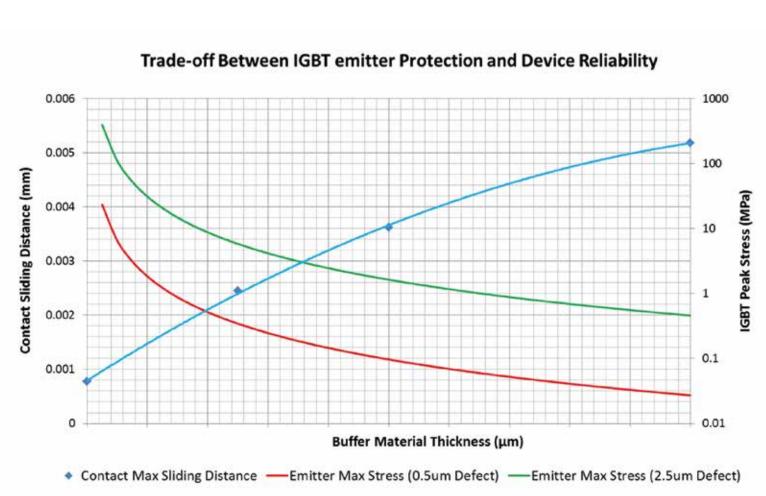

- Introducing a softer buffer between the molybdenum and IGBT emitter improves both yield and electrical performance.

- 2D axisymmetric FEM simulation of defect indentation demonstrates how localised stresses may be redistributed.

- Buffer material has higher CTE than Silicon IGBT and Molybdenum Strain Buffer which may affect reliability.

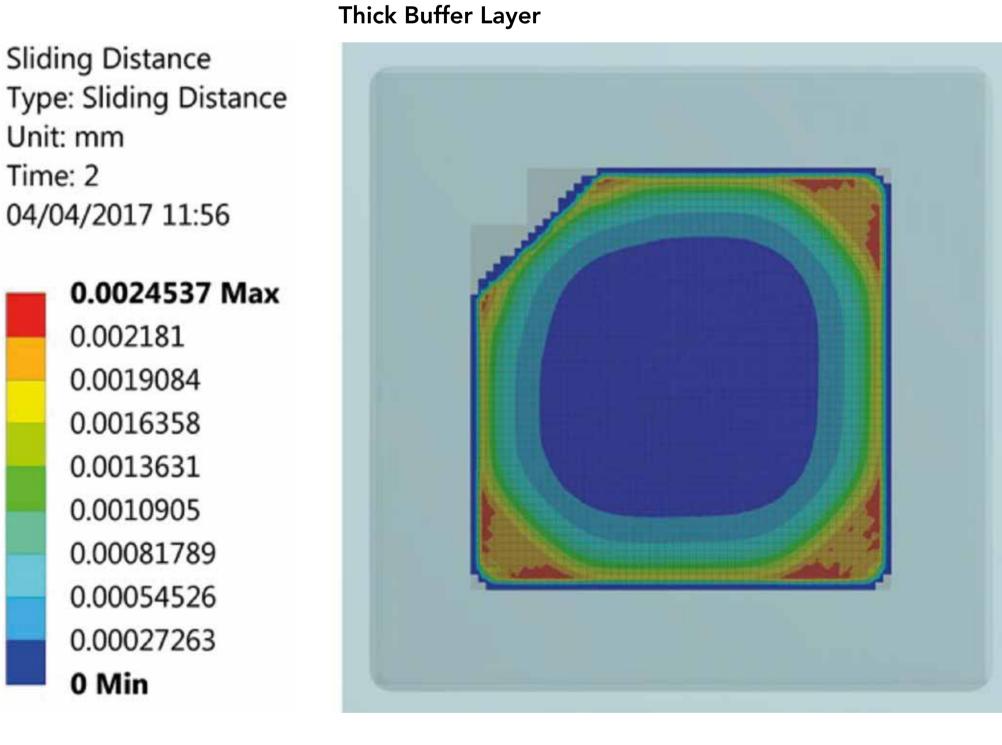

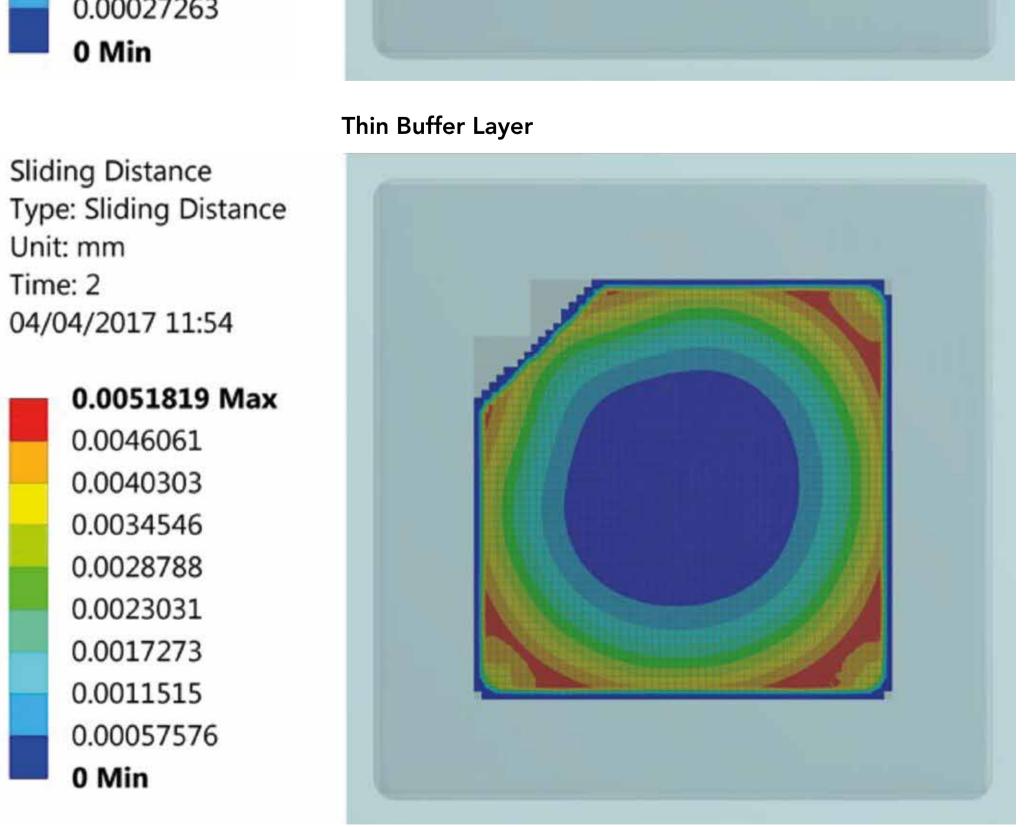

- Sliding distance used as metric for wear rate from Archards equation.

- 3D Transient thermal-structural FEM highlights how the sliding distance across the emitter surface changes with increasing buffer layer thickness.

- The trade off between IGBT surface protection, which correlates to switching performance, and reliability is demonstrated. Careful consideration must be paid to design and product requirements.

Sliding Distance

04/04/2017 11:54

0.0046061

0.0040303

0.0034546

0.0028788

0.0023031

0.0017273

0.0011515

0 Min

0.00057576

0.0051819 Max

Unit: mm

Time: 2

# Thermo-Mechanical Optimisation of Press Pack IGBT Packaging using Finite Element Method Simulation

Michael Varley, Ashley Plumpton, Chas Tonner, Robin Simpson

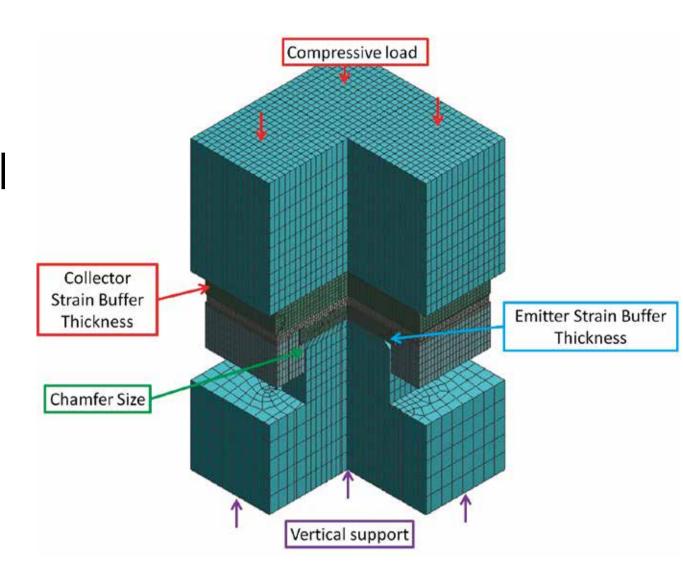

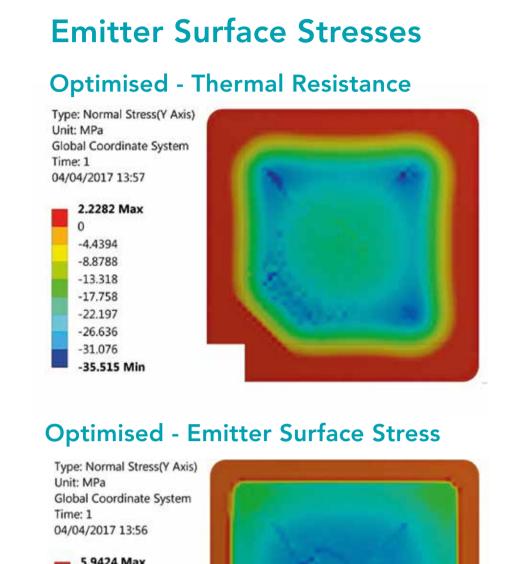

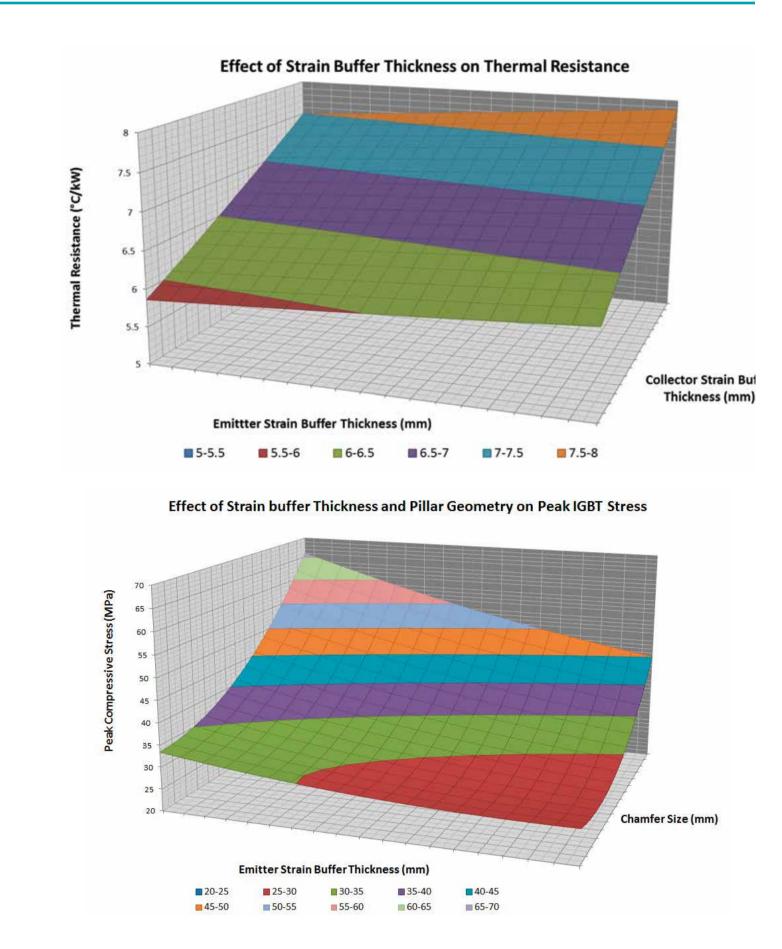

### Cassette Level Optimisation

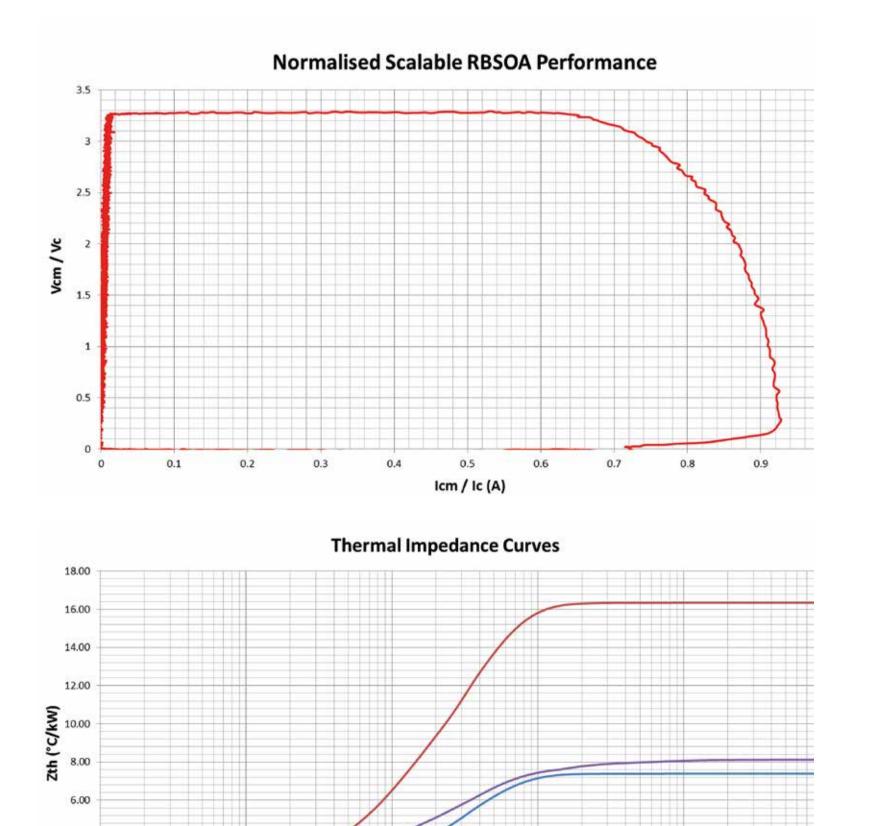

- Cassette level optimisation focuses on stress across the individual IGBT improve cassette yield and electrical performance.

- Parameterised FEM provides response surface for optimisation.

- Key performance indicators are:

- Peak Stress

- Thermal resistance

- Stress Range

-3.1452

-6.2903 -9.4355 -12.581 -15.726 -18.871 -22.016

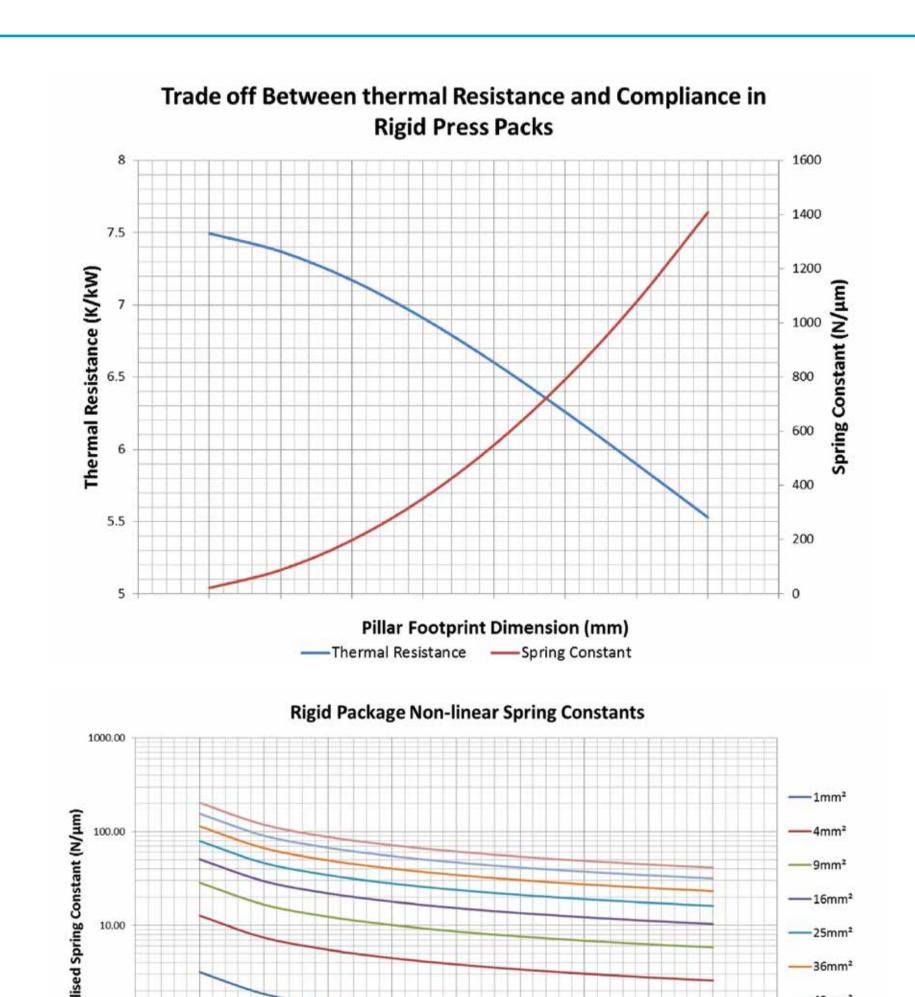

## Package Level Optimisation

- Package level optimisation requires consideration of compliance to accommodate component tolerances and providing an effective cooling solution.

- There are two packaging concepts: 'rigid' and compliant

- Rigid devices offer double side cooling.

- Compliant devices offer spring constants several orders of magnitude smaller than rigid devices.

- Assuming linear elastic response, in order to have a meaningful contribution from the emitter side cooling, pillar geometry the results in a spring constant over  $1000N/\mu m$  is required.

- Given the tolerances of the Press Pack components the rigid device will experience plastic deformation under clamping load.

- Even factoring in plastic deformation, the rigid package cannot meet a compliant designs tolerance for component variations.

### Conclusions

Development of Press Pack IGBTs is a multifaceted process. There are three key considerations:

- 1. Optimising IGBT protection vs reliability

- 2. Optimising IGBT stress vs Thermal resistance

- 3. Optimising Packaging compliance vs thermal resistance

Points 1 and 2 may be considered by FEM simulation, however, packaging design should be considered on an application basis

- Compliant designs offer the best switching performance and therefore are required for the highest current ratings.

- Rigid Packages are appropriate for small diameter packages e.g. GTO replacements.

# Sample Data